# Plasma-dicing: a device-enabling technology for advanced packaging and 3D integration.

<u>Philippe Bézard,</u> Julien Vitiello, Swann Ferrand, Maximilien Cottat, Thierry Lazerand

MINAPAD Session: Dicing / Picking 1 Grenoble, France May, 22nd 2019

Plasma-Therm Confidential ©2019 All Rights Reserved

### Outline

1. Limitations of the current dicing technologies and motivations

2. Integrating Plasma dicing in a 3D packaging flow.

1. Limitations of the current dicing technologies and motivations

2. Integrating Plasma dicing in a 3D packaging flow.

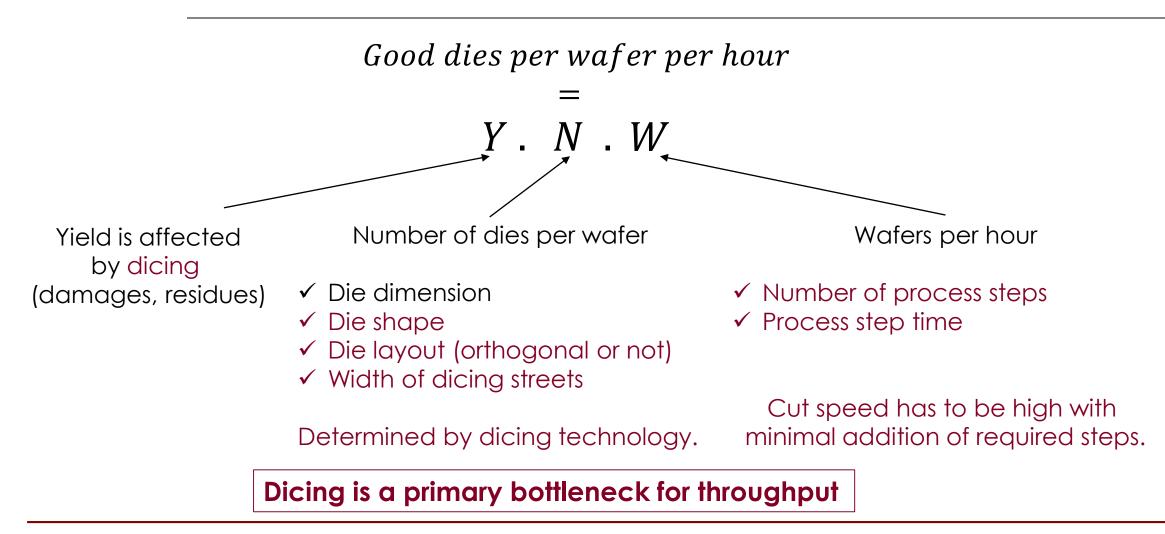

### Motivations – What do we want?

### Identifying bottlenecks for throughput

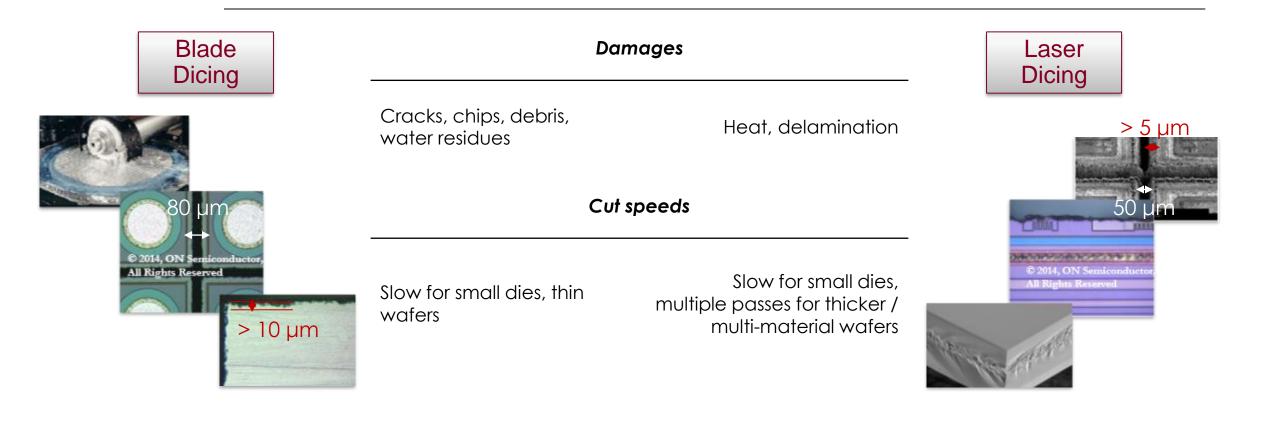

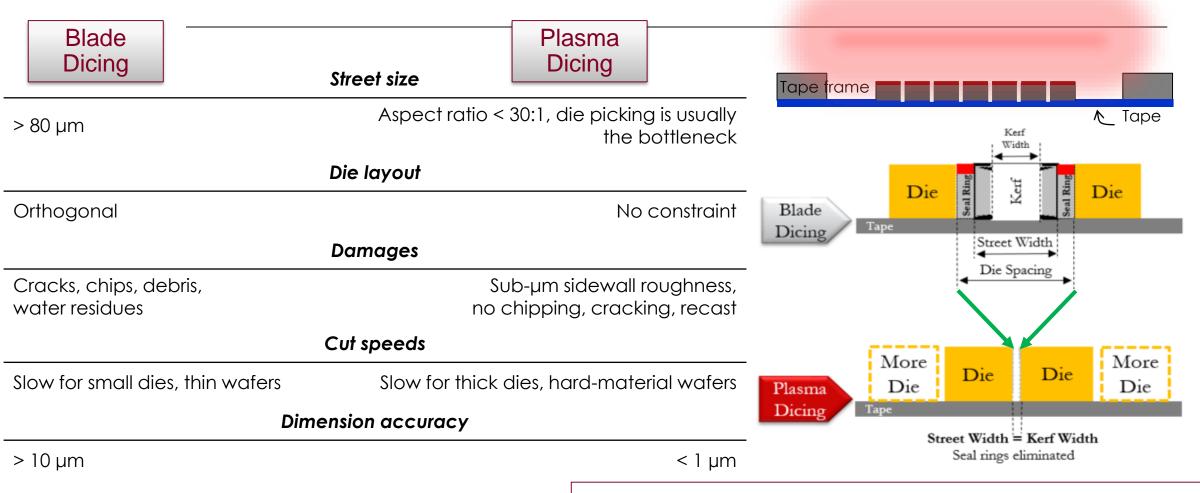

### Wafer Dicing Technology limits

Sequential mechanical / thermal processes limited by beam/ blade dimensions

### Parallel + chemical dicing technology: plasma dicing

Highest die density and best quality with plasma

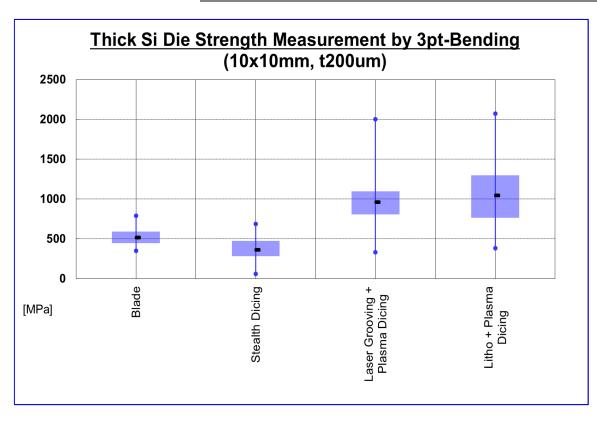

Impact on die strength

- Thick die -> sidewall contributions to the die strengths are large

- Sidewall quality correlates to die strengths

- Plasma dicing improves die strengths for thick dies

$\delta = \frac{3LW}{2bh^2}$

W

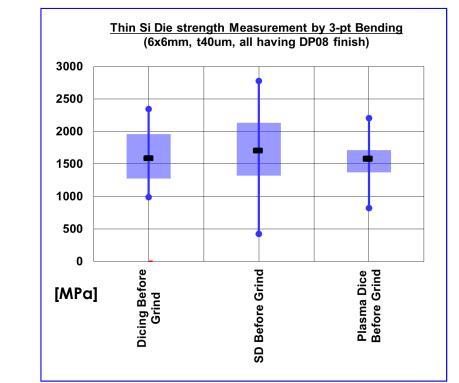

- When die is thin, sidewall contributions to die strengths diminishes

- Wafer backside finish quality dominates die strengths

- Same wafer backside finish → similar thin die strengths

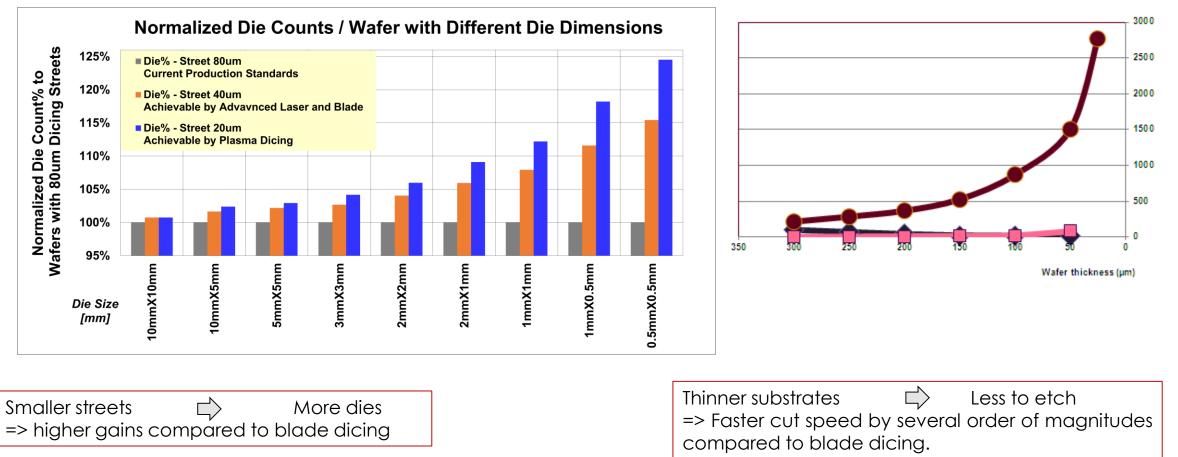

### Impact on throughput

### Throughput and Cost of ownership

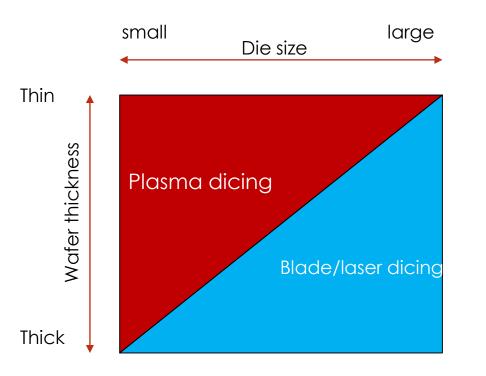

Better CoO with plasma dicing for small dies / thin wafers compared to blade dicing

-> complementary approach in terms of CoO.

Even when the CoO is worse with plasma dicing, some applications may need the best quality available.

# Plasma Dicing – Integrating FEOL into BEOL

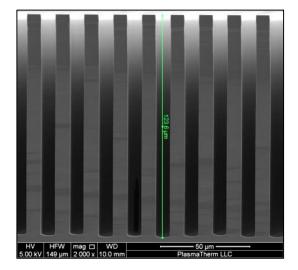

#### Three-step "Bosch" process

Passivation  $(C_4F_8 \rightarrow (CF_2)_n)$ Deposition Selective passivation ↑ Tape removal Etch A Scallop Depth Scallop Length Isotropic etching of Si  $(SF_6)$ Most common trade-offs (dicing quality vs throughput) are: Etch B Large scallop depths vs etch rate Large scallop aspect ratio vs selectivity.

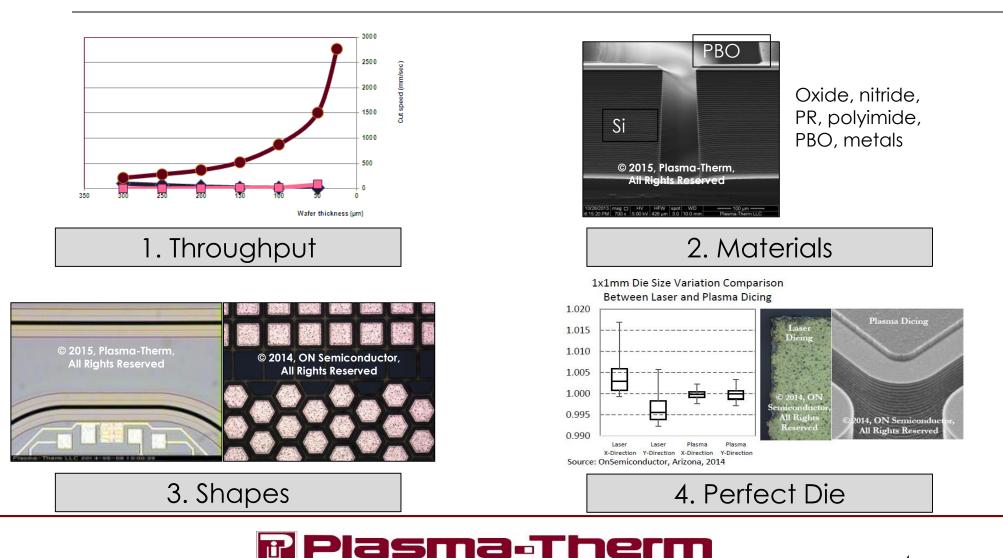

### Typical performance of plasma dicing processes

#### Ultra-low damage

Tape temperature is ~60°C (low thermal), no mechanical action

#### **Materials**

High selectivity with SiO2 (1000:1), PR ( > 250:1), possible to etch with metals exposed

#### Die shapes

Litho-defined

Cut speeds

Typically 25-30  $\mu m$  / min for Silicon

**Dimension accuracy**

Litho-defined (~100 nm)

Performance looks promising (5 min-long process for a common 150 um-thick wafer). Optional additional mask (SiO/N passivation is enough)

What about the die strength?

1. Limitations of the current dicing technologies and motivations

2. Integrating Plasma dicing in a 3D packaging flow.

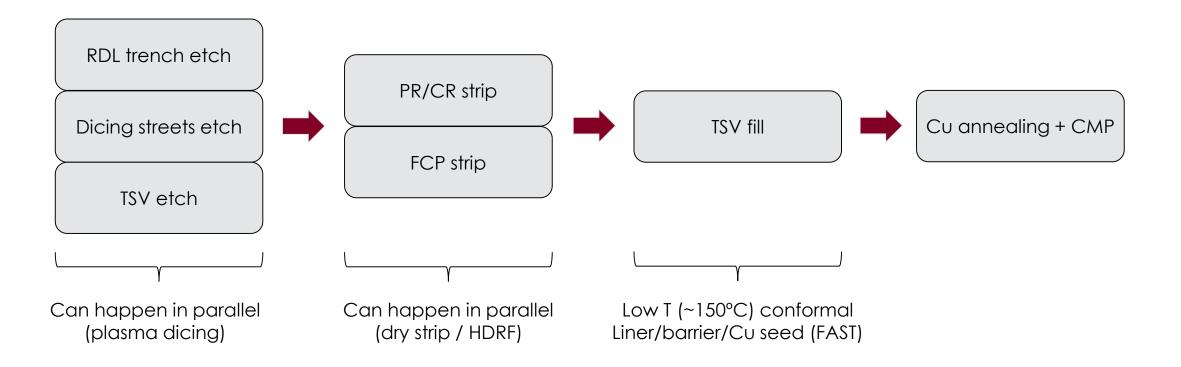

### Plasma dicing in a Damascene RDL process flow

Damascene process flow allows higher RDL density, sub-micron L&S. Plasma dicing and other key technologies allow parallelizing steps.

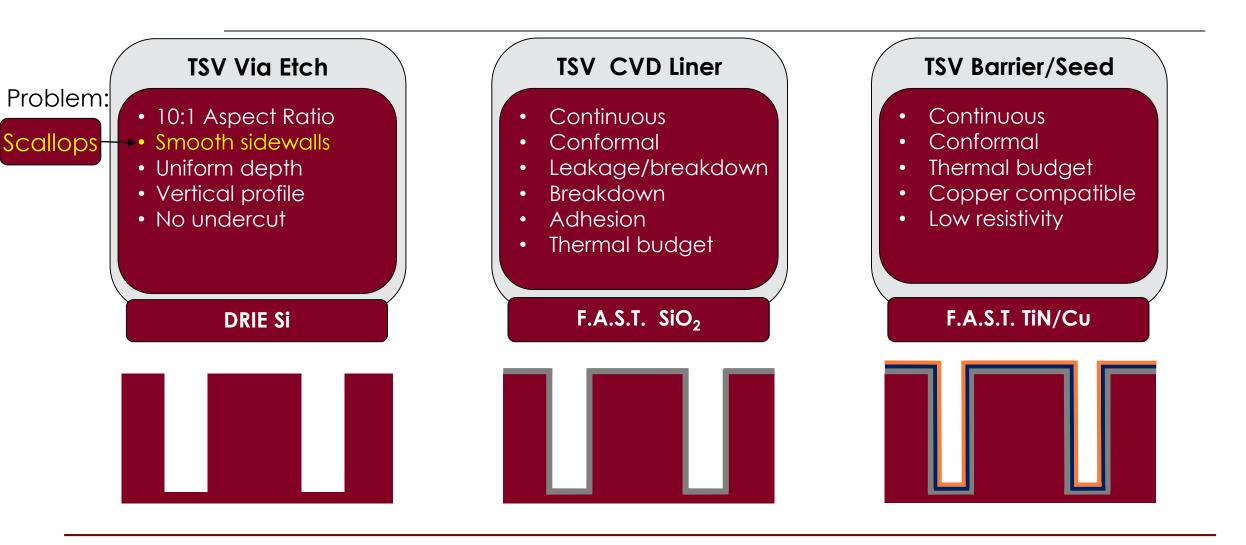

### Bonus of plasma dicing – TSV etching during dicing

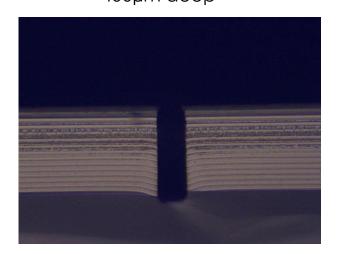

#### 15µm Trench diameter 400µm deep

High rate

**8µm Via diameter** 120µm deep

Vertical profile

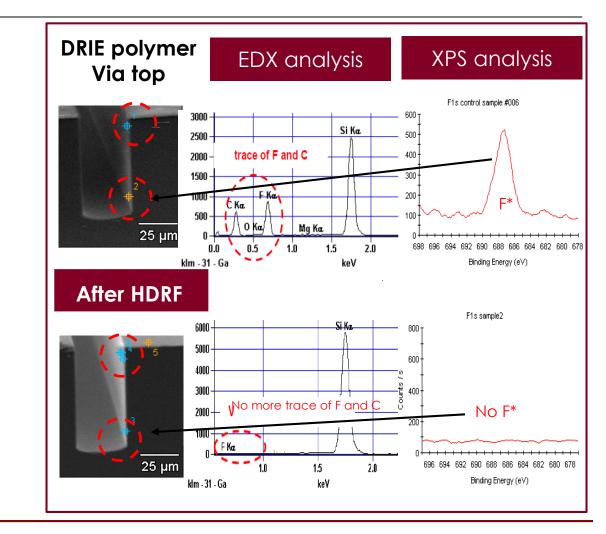

Fluorocarbon polymer needs to be removed before TSVs can be filled.

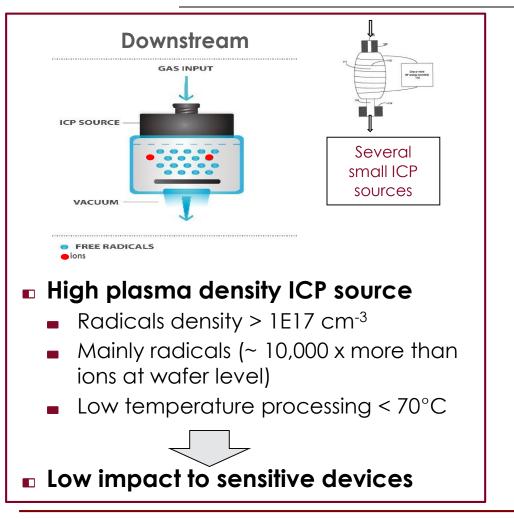

# HDRF: Efficient fluorocarbon polymer removal

# Low Temperature Processes for TSV Integration

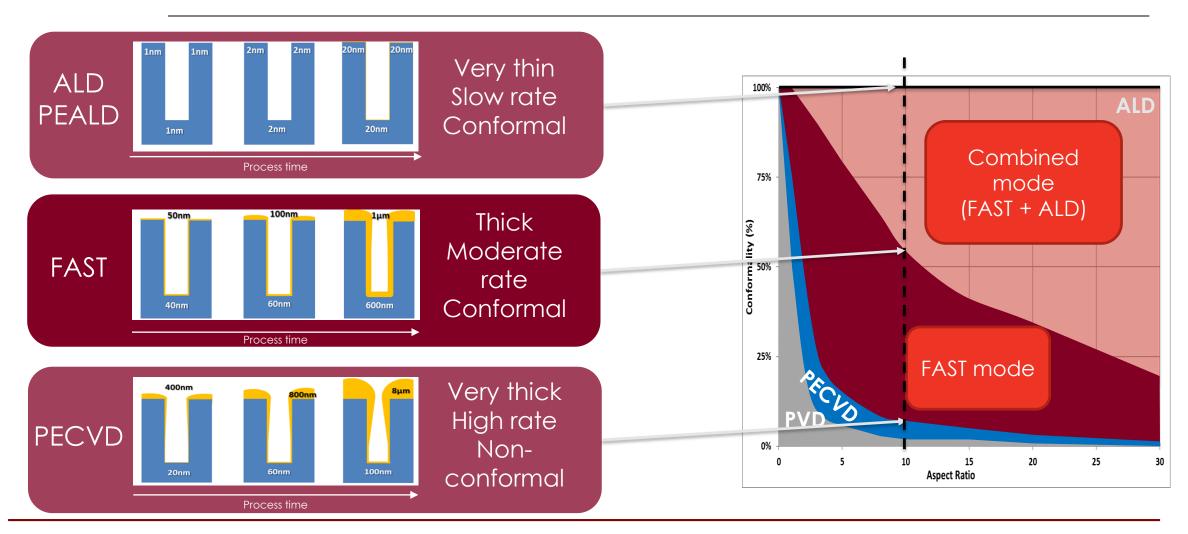

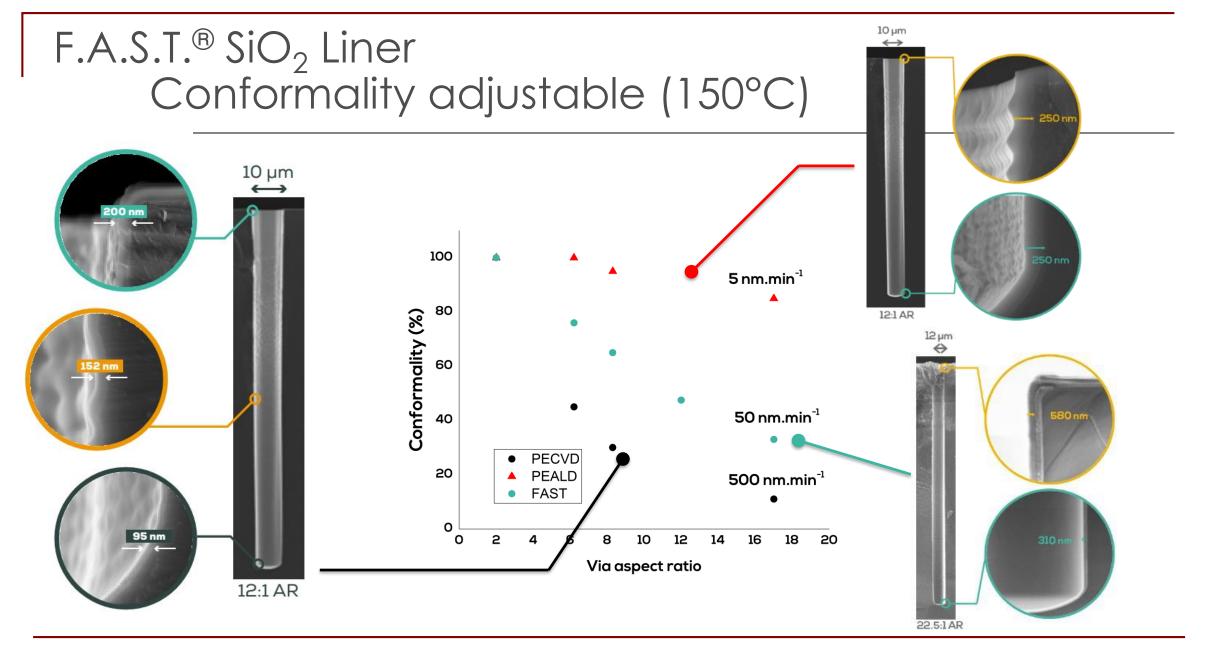

# Liner Technology Approaches for TSV

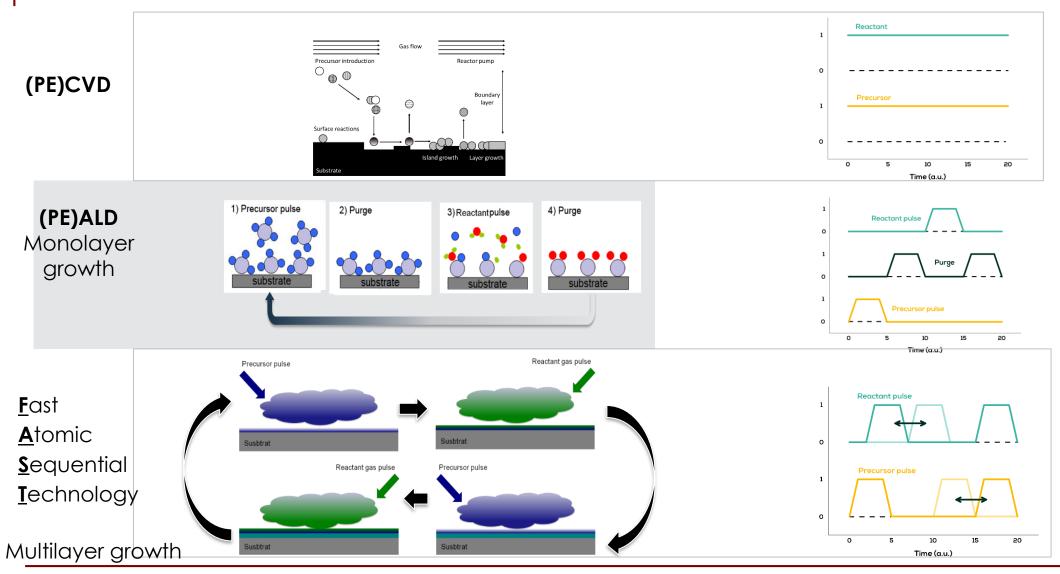

### F.A.S.T.® Crossroads of ALD and CVD

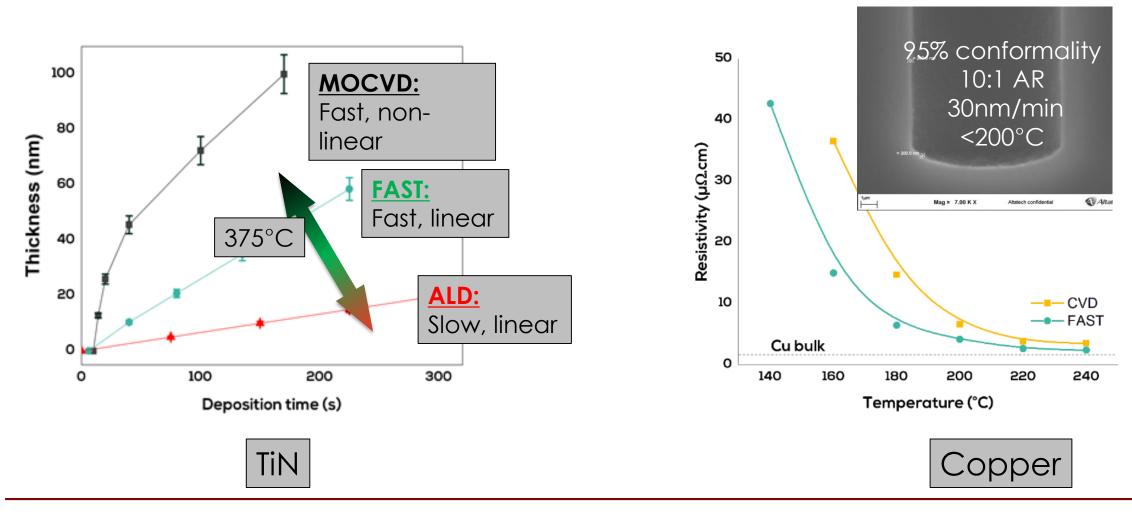

### TiN and Cu example with FAST

# Conclusion

- Plasma dicing is a complementary technology: laser ablation/stealth and saw dicing will not be replaced, only new devices will now be possible.

- Top-notch dicing quality if requirements are extreme.

- 3D/hybrid packaging process flows benefit a lot from plasma dicing.

# Thank you for your attention!

This project has received funding from the Electronic Component Systems for European Leadership Joint Undertaking under grant agreement No 737497. This Joint Undertaking receives support from the European Union's Horizon 2020 research and innovation programme and Portugal, Austria, Netherlands, Finland, Germany, Hungary, Ireland, France, and Sweden.

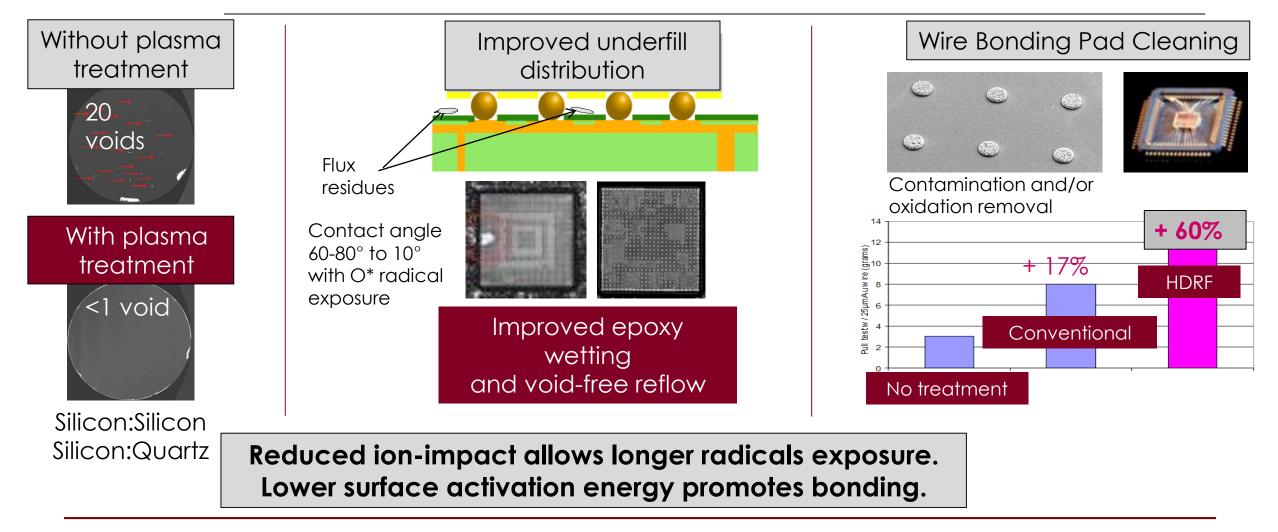

#### Surface Activation/Cleaning for Wafer Bonding High O\* exposure without ions, UV or high temp